In a recent blog post, Intel made bold claims about its new PowerVia technology and its performance on a Meteor Lake-based test chip, with a clock speed increase of over 5%. According to Ben Sell, Intel's vice president of technology development, PowerVia will be available next year along with the Intel 20A process node.

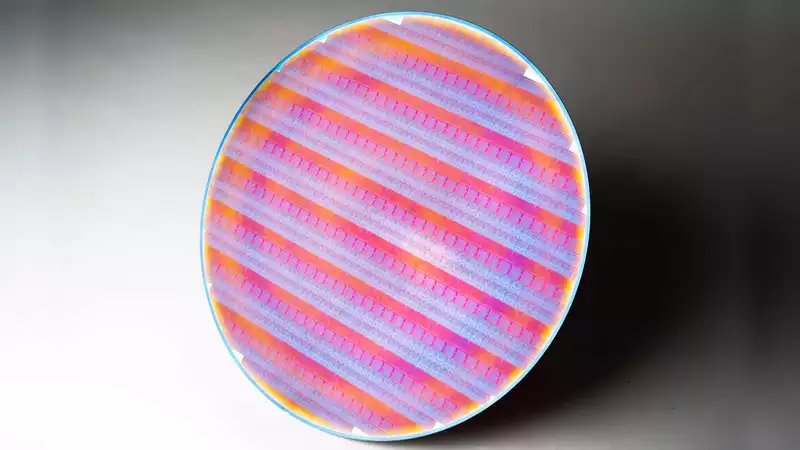

PowerVia represents a new way of making processors, in effect sandwiching the transistors in the middle of the chip, with the interconnections to the outside world at the front and the power routing at the back. This so-called backside power delivery is a major shift in semiconductor manufacturing, while at the same time simplifying, complicating, and mitigating the ever-shrinking problem of transistors and processors.

PowerVia will be first sampled in the next Arrow Lake generation of Intel processors (probably 15th generation Core), scheduled for 2024 on the Intel 20A manufacturing process. However, in order to speed up the development process, the 20A process node was decoupled from the design itself.

Indeed, Intel demonstrated the functional advantages of this technology with a "Frankenstein test chip" called Blue Sky Creek. It is actually a Meteor Lake-based chip using the next-generation Efficient core manufactured on the Intel 4 process, but incorporating PowerVia technology.

Intel claims to have successfully added a frequency increase of more than 5% to the test chip just by adding backside power delivery; using the Raptor Lake E core's clock speed as a starting point, simply changing the location of interconnect and power routing can increase the frequency from 4.3GHz to 4.5GHz.

Traditionally, chips are built like a pizza (Intel's words, not mine), with the core transistors at the bottom and everything else stacked on top. It is then flipped over and placed in a package that fits into a socket on the motherboard to maintain the connection to the outside world.

Backside power delivery, or in Intel's PowerVia, is like a sandwich. There is a transistor in the middle, an interconnect layer on top, and a power connection on the backside of the transistor.

This is a vast oversimplification of what Intel has done with PowerVia, but it actually means that there is room for larger connections over larger distances. As transistors continue to shrink and more transistors are crammed onto chips, the massive amount of power and interconnect wiring stacked on top of the pizza chip means interference, power and signal fade out in chaos.

The simplicity inherent in separating things out is as beneficial to power as it is to interconnects.

Intel is not alone in doing this. Backside power delivery is something all chipmakers are considering as nodes get smaller. However, Intel claims that PowerVia coming online with its 20A process RibbonFET (or gate all-around) technology will put it "roughly two years behind" its competitors on backside power delivery.

Comments