Chiplet technology has been fully integrated into the CPU world with Zen 4 and Raptor Lake, but it has yet to reach graphics cards. But that will change with AMD's upcoming RDNA 3 GPUs, the RX 7900 XTX and RX 7900 XT (open in new tab), which will bring chiplets to gaming graphics, which required the Red Team to rethink its entire interconnect technology.

AMD may have mastered chiplets for CPUs, but to get more performance out of chiplet-based GPUs, more connections needed to be shrunk into even smaller spaces. This is where the new fan-out technology AMD is introducing in RDNA 3, called Infinity Links, comes in.

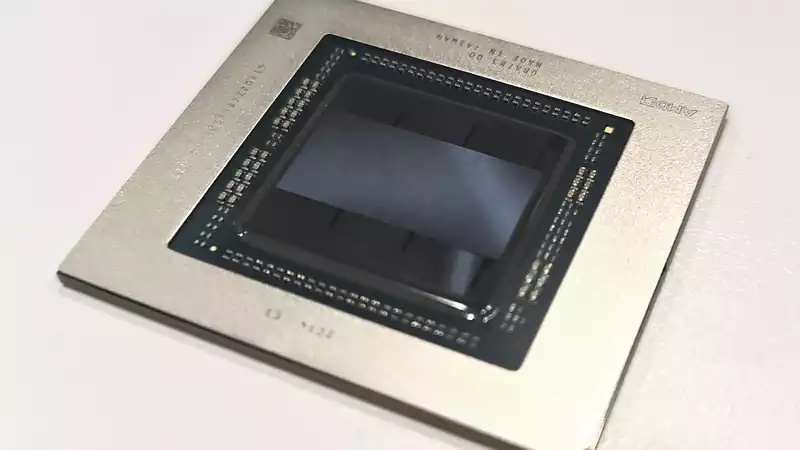

The Infinity Links fan-out is used to connect the GCD die (core graphics engine) of AMD's Navi 31 GPU package to the MCD die (up to six) that contains the GDDR6 memory interface and Infinity Cache. This allows AMD to achieve a peak bandwidth of 5.3 TB/s, almost 10 times the bandwidth density of the links used in Ryzen and Epyc CPUs. [The massive 5.3 terabytes/second figure announced this morning means that each of these interfaces (MCDs) has four 64-byte channels in both directions. This is a huge number of wires. An organic package cannot host this number of wires," said AMD Fellow Sam Nafziger. [We needed new packaging and linking technology. And that's what we implemented. We called it Infinity Link, and it's based on a new high-performance fan-out implementation technology that we developed with our suppliers"

.

Infinity Links works by replacing the traditional trace routing (a layout of fine wires connecting multiple parts of a chip package) with a much smaller one. Indeed, it is quite puzzling how small the Infinity Link package is compared to standard solutions.

Below: on the left is a traditional organic fanout, taken from one of AMD's server products; AMD is assuming the Epyc processor, but has not revealed which processor. On the right is the new Infinity Link fan-out; AMD says the image is almost to scale.

"The bandwidth density we've achieved is almost 10x," Naffziger continues. Naffziger continues. This was achieved at a bit rate of 9.2 gigabits per second of signal transmitted across this entire interface." Also, by making the bumps finer pitched and single routed, the bandwidth density can be dramatically increased. [This interconnect is critical to the overall RDNA 3 chiplet architecture and is not entirely unworkable. [However, given the power efficiency of the entire RDNA 3 architecture, the Infinity Links also needed to be power efficient. The "aggressive clock gating" and focus on low-voltage operation is reportedly up to 80% more efficient than organic package links

. [As a result, the GPU consumes less than 5% less power and achieves 3.5 TB/sec.

However, in offering such a chiplet approach, AMD admits that latency has increased somewhat. Latency here means slower time to deliver new frames to the monitor, which may threaten the benefits of chiplet architecture in gaming GPUs in the first place.

To combat the increased latency, AMD focused on increasing the clock rate and tried to negate the increased latency in sending data from the GCD die to one of the MCD dies. [AMD feels that this is an effective trade-off, and one can only hope that this gamble pays off in terms of frames per second, with an eye toward achieving higher clocks and efficiencies with the two upcoming RDNA 3 graphics cards. The RX 7900 XTX and RX 7900 XT will be available on December 13. That means we can soon see what the world's first chiplet gaming GPUs can offer with their shiny new technologies (opens in new tab).

.

Comments